SILICON STAR INTERNATIONAL, INC.

VL-BUS 486 MAIN BOARD

|

Processor |

80486SX/80487SX/80486DX/80486DX2 |

|

Processor Speed |

25/33/40/50(internal)/50/66(internal)MHz |

|

Chip Set |

UNI |

|

Max. Onboard DRAM |

32MB |

|

Cache |

64/128/256KB |

|

BIOS |

AMI/Award |

|

Dimensions |

330mm x 218mm |

|

I/O Options |

32-bit VESA local bus slots (2) |

|

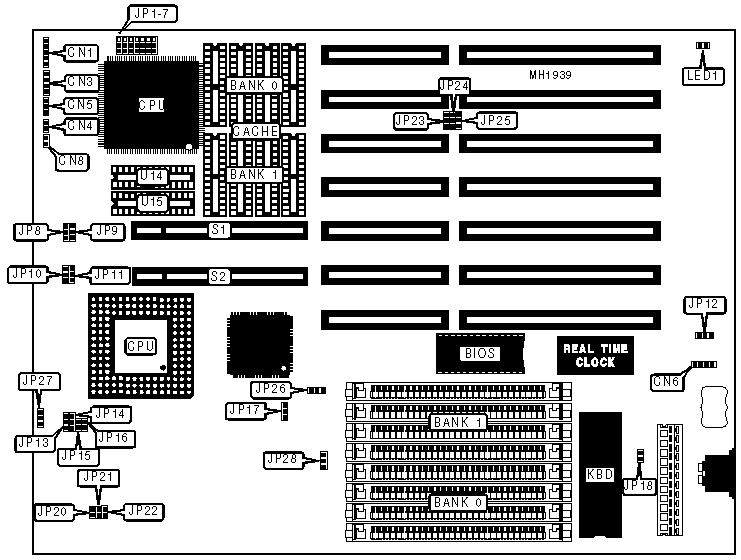

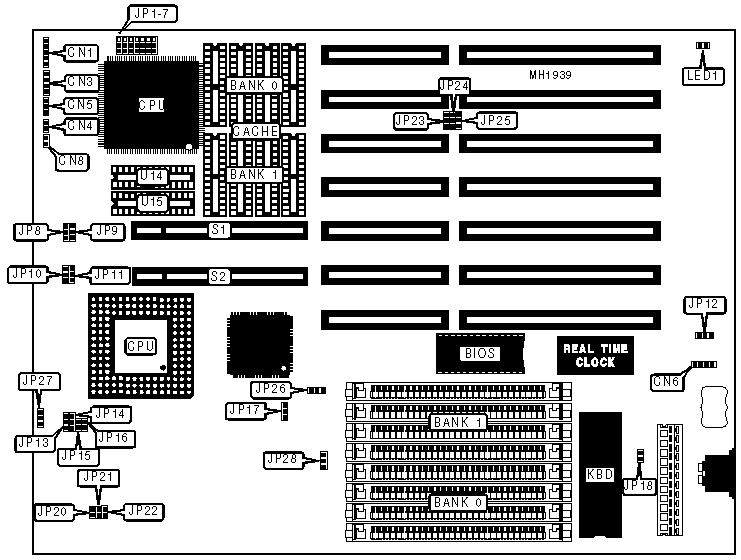

CONNECTIONS | |||

|

Purpose |

Location |

Purpose |

Location |

|

Power LED & keylock |

CN1 |

External battery |

CN6 |

|

Speaker |

CN3 |

Reset switch |

CN8 |

|

Turbo LED |

CN4 |

Power LED |

LED1 |

|

Turbo switch |

CN5 |

32-bit VESA local bus slots |

S1 & S2 |

|

USER CONFIGURABLE SETTINGS | |||

|

Function |

Jumper |

Position | |

|

» |

CMOS memory normal |

JP12 |

pins 1 & 2 closed |

|

CMOS memory clear |

JP12 |

pins 2 & 3 closed | |

|

» |

FAST A20 enabled |

JP17 |

pins 1 & 2 closed |

|

FAST A20 disabled |

JP17 |

pins 2 & 3 closed | |

|

» |

Monitor type select color |

JP18 |

Closed |

|

Monitor type select monochrome |

JP18 |

Open | |

|

» |

Factory configured - do not alter |

JP23 |

pins 1 & 2 closed |

|

» |

Factory configured - do not alter |

JP24 |

pins 1 & 2 closed |

|

» |

Factory configured - do not alter |

JP25 |

pins 1 & 2 closed |

|

» |

Factory configured - do not alter |

JP26 |

pins 2 & 3 closed |

|

» |

Power good signal detect from power supply |

JP27 |

pins 2 & 3 closed |

|

Power good signal detect from board |

JP27 |

pins 1 & 2 closed | |

|

» |

Factory configured - do not alter |

JP28 |

pins 2 & 3 closed |

|

DRAM CONFIGURATION | ||

|

Size |

Bank 0 |

Bank 1 |

|

1MB |

(4) 256K x 9 |

NONE |

|

2MB |

(4) 256K x 9 |

(4) 256K x 9 |

|

4MB |

(4) 1M x 9 |

NONE |

|

8MB |

(4) 1M x 9 |

(4) 1M x 9 |

|

16MB |

(4) 4M x 9 |

NONE |

|

32MB |

(4) 4M x 9 |

(4) 4M x 9 |

|

CACHE CONFIGURATION | ||||

|

Size |

Bank 0 |

Bank 1 |

TAG write through U15 |

TAG write back U14,U15 |

|

64KB |

(4) 8K x 8 |

(4) 8K x 8 |

8K x 8 |

(2) 8K x 8 |

|

128KB |

(4) 32K x 8 |

NONE |

8K x 8 |

(2) 8K x 8 |

|

256KB |

(4) 32K x 8 |

(4) 32K x 8 |

32K x 8 |

(2) 32K x 8 |

|

CACHE JUMPER CONFIGURATION | |||||||

|

Size |

JP1 |

JP2 |

JP3 |

JP4 |

JP5 |

JP6 |

JP7 |

|

64KB write through |

N/A |

N/A |

1 & 2 |

1 & 2 |

2 & 3 |

1 & 2 |

1 & 2 |

|

64KB write back |

1 & 2 |

1 & 2 |

1 & 2 |

1 & 2 |

2 & 3 |

1 & 2 |

1 & 2 |

|

128KB write through |

N/A |

N/A |

2 & 3 |

1 & 2 |

1 & 2 |

1 & 2 |

2 & 3 |

|

128KB write back |

2 & 3 |

1 & 2 |

2 & 3 |

1 & 2 |

1 & 2 |

1 & 2 |

2 & 3 |

|

256KB write through |

N/A |

N/A |

2 & 3 |

2 & 3 |

2 & 3 |

2 & 3 |

2 & 3 |

|

256KB write back |

2 & 3 |

2 & 3 |

2 & 3 |

2 & 3 |

2 & 3 |

2 & 3 |

2 & 3 |

|

Note:Pins designated should be in the closed position. | |||||||

|

CPU SPEED CONFIGURATION | |||

|

Speed |

JP20 |

JP21 |

JP22 |

|

25MHz |

Closed |

Open |

Closed |

|

33MHz |

Open |

Closed |

Closed |

|

40MHz |

Closed |

Open |

Open |

|

50iMHz |

Closed |

Open |

Closed |

|

50MHz |

Open |

Closed |

Open |

|

66iMHz |

Open |

Closed |

Closed |

|

CPU TYPE CONFIGURATION | ||||

|

CPU Type |

JP13 |

JP14 |

JP15 |

JP16 |

|

80486SX PGA |

open |

pins 2 & 3 closed |

Open |

Closed |

|

80486 SX PQFP |

open |

pins 2 & 3 closed |

Open |

Open |

|

80487SX |

pins 2 & 3 closed |

pins 1 & 2 closed |

Closed |

N/A |

|

80486DX, DX2 |

pins 1 & 2 closed |

pins 1 & 2 closed |

Closed |

N/A |

|

VESA WAIT STATE/BUS SPEED CONFIGURATION | |||||

|

CPU speed |

Wait states |

JP8 |

JP9 |

JP10 |

JP11 |

|

< 33MHz |

0 wait states |

pins 1 & 2 |

pins 1 & 2 |

pins 1 & 2 |

pins 1 & 2 |

|

> 33MHz |

1 wait state |

pins 2 & 3 |

pins 2 & 3 |

pins 2 & 3 |

pins 2 & 3 |

|

Note: Pins designated should be in the closed position. | |||||