RAD DATA COMMUNICATIONS

FCD-E1/2/E1

|

Card Type |

CSU/DSU |

|

Chip Set |

Unidentified |

|

I/O Options |

AC power connector, 25-pin connectors (2 RS-530), BNC connectors (4) 9-pin serial ports (2 RS-232), E1 network interface via RJ-48 connectors (4) |

|

E1 Transfer Rate |

2.048Kbps |

|

E1 Protocol |

HDB3 |

|

Frame type |

CRC-4 |

|

Data Bus |

External |

|

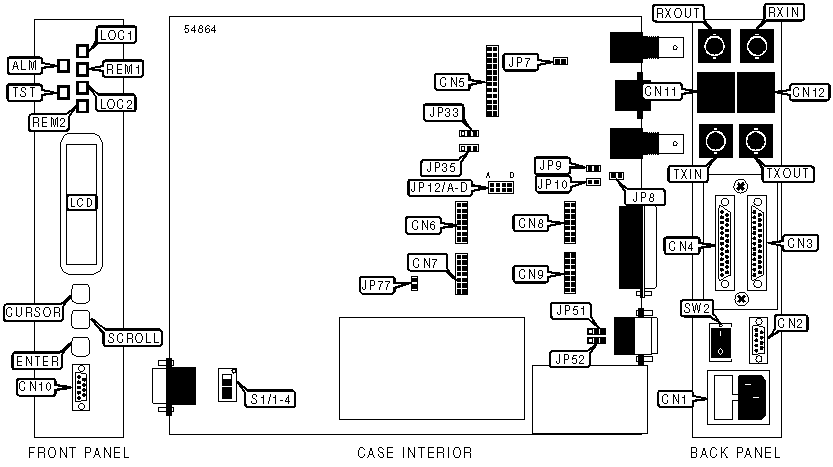

CONNECTIONS | |||

|

Function |

Label |

Function |

Label |

|

AC power connector |

CN1 |

DCE serial port |

CN10 |

|

DTE serial port |

CN2 |

Sub network port via RJ-48 connector |

CN11 |

|

Channel 1 port (25-pin connector) |

CN3 |

Main network port via RJ-48 connector |

CN12 |

|

Channel 2 port (25-pin connector) |

CN4 |

BNC connector - unbalanced receive in |

RXIN |

|

Header connector to sub link interface board |

CN5 |

BNC connector - unbalanced receive out |

RXOUT |

|

Header connector to CH2 interface board |

CN6 |

BNC connector - unbalanced transmit in |

TXIN |

|

Header connector to CH2 interface board |

CN7 |

BNC connector - unbalanced transmit out |

TXOUT |

|

Header connector to CH2 interface board |

CN8 |

Power switch |

SW2 |

|

Header connector to CH2 interface board |

CN9 | ||

|

USER CONFIGURABLE SETTINGS | |||

|

Setting |

Label |

Position | |

| » |

Signal ground is connected to the frame ground |

JP8 |

Closed |

|

Signal ground is not connected to the frame ground |

JP8 |

Open | |

| » |

Transmit side ground reference set for balanced interface |

JP9 |

Open |

|

Transmit side ground reference set for unbalanced interface |

JP9 |

Closed | |

| » |

Receive side ground reference set for balanced interface |

JP10 |

Open |

|

Receive side ground reference set for unbalanced interface |

JP10 |

Closed | |

| » |

Front panel push-buttons enabled |

JP77 |

Open |

|

Front panel push-buttons disabled |

JP77 |

Closed | |

| » |

Supervisor ports operate according to user-defined parameters |

S1/1 |

Off |

|

CSU/DSU uses default parameters stored in its EPROM |

S1/1 |

On | |

| » |

Default password enabled. Password=RAD |

S1/2 |

On |

|

User password enabled |

S1/2 |

Off | |

| » |

Loads user-selected parameters from NVRAM on power-up |

S1/3 |

Off |

|

Loads default parameters stored in its EPROM on power-up |

S1/3 |

On | |

| » |

Factory configured - do not alter |

S1/4 |

Off |

|

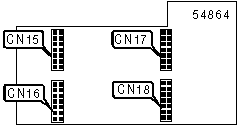

MAIN LINK INTERFACE | ||||||||

|

Function |

JP7 |

JP12/A |

JP12/B |

JP12/C |

JP12/D |

JP33 |

JP35 | |

| » |

Balanced interface |

Open |

Open |

Closed |

Open |

Open |

2 & 3 |

2 & 3 |

|

Unbalanced interface |

Closed |

Open |

Open |

Open |

Closed |

1 & 2 |

1 & 2 | |

|

Note: Pins designated are in the closed position | ||||||||

|

ALARM RELAY | |||

|

Function |

JP51 |

JP52 | |

| » |

Alarm relay disconnected. DTE port (CN2) provides full functionality |

2 & 3 |

2 & 3 |

|

Alarm relay connected instead of DCD and CTS lines |

1 & 2 |

1 & 2 | |

|

Note: Pins designated are in the closed position | |||

|

DIAGNOSTIC LED(S) | |||

|

LED |

Color |

Status |

Condition |

|

LOC1 |

Unidentified |

On |

Local synchronization lost on main link |

|

LOC1 |

Unidentified |

Off |

Local synchronization OK on main link |

|

REM1 |

Unidentified |

On |

Remote synchronization lost on main link |

|

REM1 |

Unidentified |

Off |

Remote synchronization OK on main link |

|

LOC2 |

Unidentified |

On |

Local synchronization lost on sub link |

|

LOC2 |

Unidentified |

Off |

Local synchronization OK on sub link |

|

REM2 |

Unidentified |

On |

Remote synchronization lost on sub link |

|

REM2 |

Unidentified |

Off |

Remote synchronization OK on sub link |

|

ALM |

Unidentified |

On |

Alarm condition detected on network |

|

ALM |

Unidentified |

Off |

Alarm condition not detected on network |

|

TST |

Unidentified |

On |

Device loopback test active |

|

TST |

Unidentified |

Off |

Device loopback test not running |

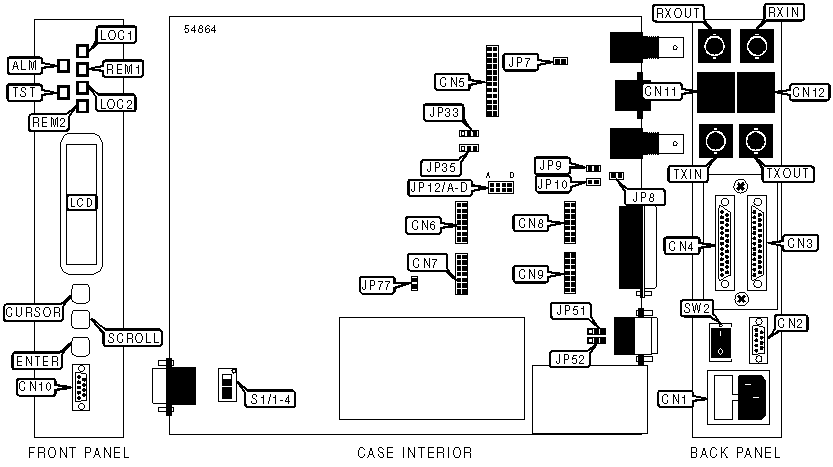

SUB LINK INTERFACE BOARD

|

CONNECTIONS | |||

|

Function |

Label |

Function |

Label |

|

Header connector to mainboard |

CN14 |

Line side protection fuse |

F3 |

|

Line side protection fuse |

F1 |

Line side protection fuse |

F4 |

|

Line side protection fuse |

F2 | ||

|

SUB LINK INTERFACE | ||||||||

|

Function |

J9 |

JP12/A |

JP12/B |

JP12/C |

JP12/D |

JP16 |

JP17 | |

| » |

Balanced interface |

Open |

Open |

Closed |

Open |

Open |

2 & 3 |

2 & 3 |

|

Unbalanced interface |

Closed |

Open |

Open |

Open |

Closed |

1 & 2 |

1 & 2 | |

|

Note: Pins designated are in the closed position | ||||||||

|

USER CONFIGURABLE SETTINGS | |||

|

Setting |

Label |

Position | |

| » |

Transmit side ground reference set for balanced interface |

JP8 |

Open |

|

Transmit side ground reference set for unbalanced interface |

JP8 |

Closed | |

| » |

Receive side ground reference set for balanced interface |

JP10 |

Open |

|

Receive side ground reference set for unbalanced interface |

JP10 |

Closed | |

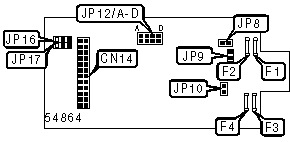

CHANNEL 2 INTERFACE BOARD

|

CONNECTIONS | |||

|

Function |

Label |

Function |

Label |

|

Header connector to mainboard |

CN15 |

Header connector to mainboard |

CN17 |

|

Header connector to mainboard |

CN16 |

Header connector to mainboard |

CN18 |